# User Guide 12C Protocol, OLED Driver

BIT-UG-0004 A

This user guide describes the I<sup>2</sup>C Interface channel setup, protocol details, and supported commands to configure and control the OLED Driver.

#### 1 Channel Configuration

Slave addresses: 0x74, 0x75

Bus speed Standard rate: up to 100 kbps

Fast Mode: up to 400 kbps

Data size 1 or 2 bytes (see specific register definitions)

# 2 Register Transactions

In all cases, the OLED Driver is ready to process an I<sup>2</sup>C command when the I<sup>2</sup>C bus is idle with SCL high (ref: Appendix A).

#### 2.1 Single byte

Single-byte parameters must be written / read in standard 1-byte protocol by performing a 1-data-byte write / read from the specified register addresses (lower address) in **bold** in Command Table.

#### 2.2 Double byte

Double-byte parameters must be written / read in standard 2-byte protocol by performing a 2-data-byte write / read from the lower of the two specified register addresses in **bold** in Command Table.

# 2.2.1 Transaction Data Formatting

# 2.2.2 Unsigned Integer

Data encoding: hexadecimal

Data size: 2 bytes (16 bits)

Lower address byte: least significant byte most significant byte

# 2.2.3 Signed Integer

Data encoding: 2's complement

Data size: 2 bytes (16 bits)

Lower address byte: least significant byte Higher address byte: most significant byte

#### 2.2.4 Unsigned Floating Point (f-p)

Data encoding: hexadecimal

Data size: 2 bytes (16 bits)

Lower address byte: fraction \* 100 Higher address byte: integer

# 2.2.5 Signed Floating Point (f-p)

Data encoding: 2's complement

Data size: 2 bytes (16 bits)

Lower address byte: fraction \* 100 Higher address byte: integer

# 3 Command Table

|          | Registe             | er Inf | fo    |        | Argument (all numerical values in decimal) |                                          |                    |                 |        |      | Description      |                                                                                                                                                              |  |  |

|----------|---------------------|--------|-------|--------|--------------------------------------------|------------------------------------------|--------------------|-----------------|--------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |                     |        |       | Size   | Factory Auto-                              |                                          |                    |                 |        |      |                  |                                                                                                                                                              |  |  |

| Label    | Addr                | r/w    | Index | (byte) | min                                        | Default (1)                              | max                | Type            | unit   | Save | Class            | Function                                                                                                                                                     |  |  |

| IVQ_INFO | 0x00                | r      | n/a   | 1      | -                                          | -                                        | -                  | binary          | n/a    | n/a  | Input<br>Control | TO   LOCK   0 = Unlocked, 1 = Locked     Gold   SDV_STAT                                                                                                     |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | [3:2] reserved - [1:0] INPUT = [0:0] INPUT = None [0:1] INPUT = SDV Analog [1:0] INPUT = SDV Digital / BT.656 [1:1] INPUT = VESA                             |  |  |

| IVQ_HA   | 0x01<br>0x02        | Г      | n/a   | 2      | -                                          | -                                        | -                  | unsigned<br>int | Pixel  | n/a  | Input<br>Control | [7:0] Least Significant byte<br>[7:0] Most significant byte                                                                                                  |  |  |

| IVQ_VA   | <b>0x03</b><br>0x04 | Γ      | n/a   | 2      | -                                          | -                                        | -                  | unsigned<br>int | line   | n/a  | Input<br>Control | [7:0] Least Significant byte<br>[7:0] Most significant byte                                                                                                  |  |  |

| IVQ_FP   | <b>0x05</b><br>0x06 | r      | n/a   | 2      | -                                          | -                                        | -                  | unsigned<br>f-p | MHz    | n/a  | Input<br>Control | [7:0] Fraction * 100<br>[7:0] Integer                                                                                                                        |  |  |

| SDVA     | 0x07                | r/w    | n/a   | 1      | 0                                          | -00, -01: <b>0</b><br>-10, -11: <b>1</b> | 1                  | unsigned<br>int | n/a    | Yes  | Input<br>Control | Set video input format for analog SDV input<br>0 = Y, CVBS, 1 = Y/C                                                                                          |  |  |

| SDVD     | 0x08                | r/w    | n/a   | 1      | 0                                          | -00, -10: <b>0</b><br>-01, -11: <b>1</b> | 1                  | unsigned<br>int | n/a    | Yes  | Input<br>Control | Set video input format for digital SDV input<br>0 = NTSC / YCbCr 4:2:2, 1 = PAL / YCbCr 4:2:2                                                                |  |  |

| BRT      | 0x09                | r/w    | n/a   | 1      | 0                                          | 8                                        | BRTMOD             | unsigned<br>int | n/a    | Yes  | Image<br>Control | Set brightness (luminance). Range = 0 ~ BRTMOD.                                                                                                              |  |  |

| BRTMOD   | 0x0A                | r/w    | n/a   | 1      | 4                                          | 16                                       | 32                 | unsigned<br>int | n/a    | Yes  | Image<br>Control | Set number of BRT adjustment steps (modulus)                                                                                                                 |  |  |

| BRTINC   | 0x0B                | w      | n/a   | 1      | 0                                          | n/a                                      | 1                  | n/a             | n/a    | n/a  | Image<br>Control | Increment BRT<br>0 = No operation, 1 = Increment BRT by 1                                                                                                    |  |  |

| BRTDEC   | 0x0C                | W      | n/a   | 1      | 0                                          | n/a                                      | 1                  | n/a             | n/a    | n/a  | Image<br>Control | Decrement BRT<br>0 = No operation, 1 = Decrement BRT by 1                                                                                                    |  |  |

| MAXLUM   | 0x0D                | r/w    | n/a   | 1      | 10                                         | 100                                      | 100                | unsigned<br>int | %      | Yes  | Image<br>Control | Set maximum display luminance, 100% = display device upper limit                                                                                             |  |  |

| GAMMA    | 0x0E<br>0x0F        | r/w    | n/a   | 2      | 1.0                                        | 1.8                                      | 2.2                | unsigned<br>f-p | exp    | Yes  | Image<br>Control | [7:0] Fraction * 100<br>[7:0] Integer                                                                                                                        |  |  |

| COLOR    | 0x10                | r/w    | n/a   | 1      | 0                                          | 4                                        | 4                  | unsigned<br>int | n/a    | Yes  | Image<br>Control | Set color mode Color OLED (BIT1011B1):                                                                                                                       |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | SDV VESA                                                                                                                                                     |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | analog digital digital Notes                                                                                                                                 |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | 0         blk/w         n/a         blk/w         digital SDV displays color           1         blk/r         blk/r         blk/r         SDV Digital: true |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | 2 blk/g blk/g blk/g monochrome only for monochrome input, else "off" 3 blk/b blk/b blk/b colors are suppressed                                               |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | 3         blk/b         blk/b         blk/b         colors are suppressed           4         color         color         n/a         VESA displays blk/wht  |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | Monochrome OLED (BIT1011B2):                                                                                                                                 |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | SDV VESA Analog Digital Digital Notes                                                                                                                        |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | 0 full luminance                                                                                                                                             |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | 1                                                                                                                                                            |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | 2 Monochrome in color of OLED luminance                                                                                                                      |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | full luminance                                                                                                                                               |  |  |

| HPOS     | <b>0x11</b><br>0x12 | r/w    | n/a   | 2      | (3) -92<br>(4) -12                         | 0                                        | (3) +92<br>(4) +12 | signed<br>int   | column | Yes  | Image<br>Control | Set horizontal image position offset 0 = default center neutral                                                                                              |  |  |

| VPOS     | <b>0x13</b><br>0x14 | r/w    | n/a   | 2      | (3) -72<br>(4) -12                         | 0                                        | (3) +72<br>(4) +12 | signed<br>int   | row    | Yes  | Image<br>Control | Set vertical image position offset 0 = default center neutral                                                                                                |  |  |

| HSCAN    | 0x15                | r/w    | n/a   | 1      | 0                                          | 0                                        | 1                  | unsigned<br>int | n/a    | Yes  | Image<br>Control | Set horizontal image scan direction 0 = normal L → R, 1 = reversed R → L                                                                                     |  |  |

| VSCAN    | 0x16                | r/w    | n/a   | 1      | 0                                          | 0                                        | 1                  | unsigned<br>int | n/a    | Yes  | Image<br>Control | Set vertical image scan direction<br>0 = normal T → B, 1 = reversed B → T                                                                                    |  |  |

| DPDC     | 0x17                | r/w    | n/a   | 1      | 1                                          | 100                                      | 100                | unsigned<br>int | %      | Yes  | Image<br>Control | Set frame duty-cycle (100% = no row blanking)                                                                                                                |  |  |

| OPATT    | 0x18                | r/w    | n/a   | 1      | 0                                          | 0                                        | 8                  | unsigned<br>int | n/a    | No   | Image<br>Control | Set OLED Driver Test Pattern 0 = No Pattern                                                                                                                  |  |  |

|          |                     |        |       |        |                                            |                                          |                    |                 |        |      |                  | 1 = White Field 2 = Color Bar 3 = Gray Scale 4 = Checker Board 5 = Vertical Lines 6 = Horizontal Lines 7 = Grid Pattern 8 = Black Field                      |  |  |

| WBCR     | <b>0x19</b><br>0x1A | r/w    | n/a   | 2      | 0                                          | 256                                      | 256                | unsigned<br>int | n/a    | Yes  | Image<br>Control | [7:0] Least Significant byte [7:0] Most significant byte 0 = 0%, <b>256 = 100</b> %                                                                          |  |  |

| WBCG     | <b>0x1B</b><br>0x1C | r/w    | n/a   | 2      | 0                                          | 256                                      | 256                | unsigned<br>int | n/a    | Yes  | Image<br>Control | 7:0] Least Significant byte   Set Green channel pixel gain:   0 = 0%, 256 = 100%                                                                             |  |  |

| WBCB     | 0x1D<br>0x1E        | r/w    | n/a   | 2      | 0                                          | 256                                      | 256                | unsigned<br>int | n/a    | Yes  | Image<br>Control | [7:0] Least Significant byte [7:0] Most significant byte  Set Blue channel pixel gain: 0 = 0%, 256 = 100%                                                    |  |  |

| VER      | 0x1F<br>0x20        | г      | n/a   | 2      |                                            | -                                        | -                  | unsigned<br>f-p | n/a    | n/a  | System           | [7:0] Fraction * 100 Read SW Version Number<br>[7:0] Integer                                                                                                 |  |  |

|          | Registe             | er In | fo    |                | Argument (all numerical values in decimal) |                                            |     |                 |      |               |        | Description                                                       |                        |  |  |

|----------|---------------------|-------|-------|----------------|--------------------------------------------|--------------------------------------------|-----|-----------------|------|---------------|--------|-------------------------------------------------------------------|------------------------|--|--|

| Label    | Addr                | r/w   | Index | Size<br>(byte) | min                                        | Factory<br>Default (1)                     | max | Туре            | unit | Auto-<br>Save | Class  | Function                                                          |                        |  |  |

| POWER    | 0x21                | r/w   | n/a   | 1              | 0                                          | 1                                          | 1   | unsigned<br>int | n/a  | Yes           | System | Set power mode 0 = powered-down (low-power), 1 = operational      |                        |  |  |

| LEDEN    | 0x22                | r/w   | n/a   | 1              | 0                                          | 1                                          | 1   | unsigned<br>int | n/a  | Yes           | System | Set LED enable: 0 = Status LEDs disabled, 1 = Status LEDs enabled |                        |  |  |

| OMONOCHR | 0x23                | r/w   | n/a   | 1              | 0                                          | BIT1011B1: <b>0</b><br>BIT1011B2: <b>1</b> | 1   | unsigned<br>int | n/a  | Yes           | System | Set OLED type:<br>0 = Color XL, 1 = Monochrome Green XLT          |                        |  |  |

| ОТЕМР    | <b>0x24</b><br>0x25 | г     | n/a   | 2              | n/a                                        | n/a                                        | n/a | signed<br>f-p   | °C   | n/a           | System | [7:0] Fraction * 100<br>[7:0] Integer                             | Query OLED Temperature |  |  |

| OLEDSN_0 | 0x26                | r     | n/a   | 1              | n/a                                        | n/a                                        | n/a | ASCII           | n/a  | n/a           | System | Returns OLED Serial Number Char 1 (Leftmost)                      |                        |  |  |

| OLEDSN_1 | 0x27                | r     | n/a   | 1              | n/a                                        | n/a                                        | n/a | ASCII           | n/a  | n/a           | System | Returns OLED Serial Number Char 2                                 |                        |  |  |

| OLEDSN_2 | 0x28                | г     | n/a   | 1              | n/a                                        | n/a                                        | n/a | ASCII           | n/a  | n/a           | System | Returns OLED Serial Number Char 3                                 |                        |  |  |

| OLEDSN_3 | 0x29                | г     | n/a   | 1              | n/a                                        | n/a                                        | n/a | ASCII           | n/a  | n/a           | System | Returns OLED Serial Number Char 4                                 |                        |  |  |

| OLEDSN_4 | 0x2A                | r     | n/a   | 1              | n/a                                        | n/a                                        | n/a | ASCII           | n/a  | n/a           | System | Returns OLED Serial Number Char 5 (Righftmost)                    |                        |  |  |

<sup>(1)</sup> Factory Default values overwritten upon change by auto-save function.

#### 4 Detailed Register Descriptions

# 4.1 Input Control Registers

# 4.1.1 IVQ\_INFO

Register address: **0x00**Access type: read-only

Data type: single byte

Function: Reads input video status information.

[7] SDV\_LOCK Indicates lock status of analog SDV decoder

0 = unlocked 1 = locked

[6] reserved

[5:4] **SDV\_STAT** Indicates SDV input detection status

[00] None Detected[01] NTSC Detected[10] PAL Detected[11] reserved

[3:2] reserved

[1:0] **INPUT** Indicates INPUT configuration

[00] INPUT = None

[01] INPUT = SDV - Analog

[10] INPUT = SDV - Digital (BT.656)

[11] INPUT = VESA

# 4.1.2 IVQ\_HA

Register addresses: **0x01**, **0x02** Access type: read-only

Data type: double byte unsigned integer

Function: Reads input video Horizontal Active period (in pixels).

4.1.3 IVQ\_VA

Register addresses: **0x03**, **0x04** Access type: read-only

Data type: double byte unsigned integer

Function: Reads input video Vertical Active period (in lines).

4.1.4 IVQ FP

Register addresses: **0x05**, **0x06** Access type: read-only

Data type: double byte floating point

Function: Reads input video Pixel Clock Frequency (in MHz).

#### 4.1.5 SDVA

Register address: **0x07**Access type: write / read single byte

Function: Sets video format for analog SDV input.

**SDVA** = 0 Monochrome: Y Color: CVBS

SDVA = 1 Color: Y/C

#### 4.1.6 SDVD

Register address: **0x08**Access type: write / read single byte

Function: Sets video format for digital SDV input (BT.656).

**SDVD** = 0 NTSC **SDVD** = 1 PAL

#### 4.2 Image Control Registers

#### 4.2.1 BRT

Register address: **0x09**Access type: write / read

Data type: single byte unsigned integer Function: Sets display luminance.

Range:  $0 \le BRT \le BRTMOD$ .

#### **4.2.2 BRTMOD**

Register address: **0x0A**Access type: write / read

Data type: single byte unsigned integer

Function: Sets the number of **BRT** steps over luminance range (modulus).

Example:

**BRTMOD** = 16

**BRT** steps = 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, **16**

#### **4.2.3 BRTINC**

Register address: **0x0B**Access type: write-only

Data type: single byte unsigned integer

Function: Increments **BRT** value by 1. If **BRT = BRTMOD**, no operation.

**BRTINC** = 0 no action **BRTINC** = 1 increment BRT

#### **4.2.4 BRTDEC**

Register address: **0x0C**Access type: write-only

Data type: single byte unsigned integer

Function: Decrements **BRT** value by 1. If **BRT = 0**, no operation.

BRTDEC = 0 no action BRTDEC = 1 decrement BRT

#### 4.2.5 MAXLUM

Register address: **0x0D**Access type: write / read

Data type: single byte unsigned integer

# BIT-UG-0004\_A

Function: Sets luminance value for **BRT = BRTMOD** as a percentage of maximum OLED

luminance.

4.2.6 **GAMMA**

Register addresses: **0x0E**, **0x0F** Access type: write / read

Data type: double byte unsigned floating-point

Function: Sets display gamma value.

Example:

**GAMMA** = 1.8 = 0x50, 0x01

4.2.7 COLOR

Register address: **0x10**Access type: write / read

Data type: single byte unsigned integer Function: Sets display color mode.

**COLOR** = 0 Monochrome:

BIT1011B1 w/ Color OLED: blk / wht

BIT1011B2 w/ Monochrome OLED: monochrome in color of OLED, full luminance

**COLOR** = 1 Monochrome

BIT1011B1 w/ Color OLED: blk / red

BIT1011B2 w/ Monochrome OLED: monochrome in color of OLED, reduced luminance

**COLOR** = 2 Monochrome

BIT1011B1 w/ Color OLED: blk / grn

BIT1011B2 w/ Monochrome OLED: monochrome in color of OLED, reduced luminance

**COLOR** = 3 Monochrome

BIT1011B1 w/ Color OLED: blk / blu

BIT1011B2 w/ Monochrome OLED: monochrome in color of OLED, reduced luminance

COLOR = 4 Color

BIT1011B1 w/ Color OLED: full color

BIT1011B2 w/ Monochrome OLED: monochrome in color of OLED, full luminance

4.2.8 HPOS

Register addresses: **0x11**, **0x12** Access type: write / read

Data type: double byte signed integer Function: Sets horizontal image position.

Negative values move image to the left, positive values move image to the right.

Unit = 1 column (pixel)

4.2.9 VPOS

Register addresses: **0x13**, **0x14** Access type: write / read

Data type: double byte signed integer Function: Sets vertical image position.

Negative values move image up, positive values move image down.

Unit = 1 row (line)

4.2.10 HSCAN

Register address: **0x15**Access type: write / read

Data type: single byte unsigned integer Function: Sets horizontal scan direction. **HSCAN** = 0 normal horizontal scan direction ( $L \rightarrow R$ )

#### **HSCAN** = 1 reverse horizontal scan direction ( $L \leftarrow R$ )

Normal scan orientation specified in product datasheet.

#### 4.2.11 VSCAN

Register address: **0x16**Access type: write / read

#### 4.2.12 DPDC

Register address: **0x17**Access type: write / read

Data type: single byte unsigned integer Function: Sets Display PWM Duty Cycle.

#### 4.2.13 OPATT

Register address: **0x18**Access type: write / read

Data type: single byte unsigned integer Function: Sets bult-in test pattern.

**OPATT** = 0 No pattern selected, input video displayed

White Field **OPATT** = 1 **OPATT** = 2 Color bar **OPATT** = 3 Grav scale Checker board OPATT = 4Vertical lines **OPATT** = 5 Horizontal lines **OPATT** = 6 OPATT = 7Grid pattern **OPATT** = 8 Black Field

### 4.2.14 WBCx

Register addresses: Red: 0x19, 0x1A

Green: **0x1B**, **0x1C** Blue: **0x1D**, **0x1E**

Access type: write / read

Data type: double byte unsigned integer

Function: With BIT1011B1 + Color OLED, sets R/G/B channel gain values of White Balance

Control.

# x = R, G, B

The White Balance Control (**WBC**) function provides a method for adjusting the R-G-B mix of video data applied to the OLED to establish a desired white chromaticity value by attenuating excessively strong color component(s). The applied R/G/B color pixel values are as follows:

RED<sub>applied</sub> = RED \* (WBCR/256) GRN<sub>applied</sub> = GRN \* (WBCG/256) BLU<sub>applied</sub> = BLU \* (WBCB/256)

With BIT1011B2 + Monochrome OLED, redudes luminance.

#### 4.3 System Registers

#### 4.3.1 VERSION

Register addresses: **0x1F**, **0x20** Access type: read-only

Data type: double byte unsigned floating-point

Function: Reads software version number.

Example (acutal SW version may vary):

Lower address byte = 0x04 Upper address byte = 0x01 SW version = 1.04

#### 4.3.2 **POWER**

Register address: **0x21**Access type: write / read

Data type: single byte unsigned integer

Function: Sets power mode.

**POWER =**0: Power down command / OLED Driver is in powered-down state

1: Power up command / OLED Driver is in operational state

#### 4.3.3 **LEDEN**

Register address: **0x22**Access type: write / read

Data type: single byte unsigned integer

Function: Sets **ACT**, **OOL** indicator LED mode.

**LEDEN** = 0 LEDs disabled LEDs enabled

#### 4.3.4 OMONOCHR

Register address: **0x23**Access type: write / read

Data type: single byte unsigned integer Function: Sets OLED compatibility type.

**OMONOCHR** = 0 Color

Monochrome Green

#### 4.3.5 OTEMP

Register address: **0x24, 0x25** Access type: read-only

Data type: double byte signed integer

Function: Reads OLED temperature (in Celsius).

Example (acutal OLED temperature will vary):

Lower address byte = 0x4C Upper address byte = 0x33 OLED Temperature = 51.76 °C

#### 4.3.6 OLEDSN\_0 ~ \_4

Register addresses: 0x26, 0x27, 0x28, 0x29, 0x2A

Access type: read-only

Data type: single byte ASCII

Function: Reads 5 character alphanumeric OLED serial number.

Example (acutal OLED SN will vary):

Lowest address byte (leftmost character) addr 0x26: 0x5A = **Z**Next address byte addr 0x27: 0x31 = **1**Next address byte addr 0x28: 0x30 = **0**Next address byte addr 0x29: 0x56 = **V**Highest address byte (rightmost character) addr 0x2A: 0x50 = **P**

OLED Serial Nuber = Z10VP

# **Contact**

Bild Innovative Technology LLC 2656 W Montrose Ave Suite 203 Chicago, IL 60618 (773) 697-9345 (760) 450-6633 pbeerdeke@bildinnotech.com

# APENDIX A I2C Bus Operation

#### A1 I<sup>2</sup>C Interface

# A1.1 General I<sup>2</sup>C Operation

The I<sup>2</sup>C bus is a standard bidirectional interface that uses a controller, known as the master, to communicate with slave devices. A slave may not transmit data unless it has been addressed by the master. Each device on the I<sup>2</sup>C bus has a specific device address to differentiate between other devices that are on the same I<sup>2</sup>C bus. Many slave devices will require configuration upon startup to set the behavior of the device. This is typically done when the master accesses the slave's internal register maps, which have unique register addresses. A device can have one or multiple registers where data is stored, written, or read.

The physical  $I^2C$  interface consists of the serial clock (SCL) and serial data (SDA) lines. Both SDA and SCL lines must be connected to  $V_{CC}$  through a pull-up resistor. The size of the pull-up resistor is determined by the amount of capacitance on the  $I^2C$ . Data transfer may be initiated only when the bus is idle. A bus is considered idle if both SDA and SCL lines are high after a STOP condition.

The general procedure for a master to access a slave device is the following:

- 1. Suppose a master wants to send data to a slave:

- Master-transmitter sends a START condition and addresses the slave-receiver

- Master-transmitter sends data to slave-receiver

- Master-transmitter terminates the transfer with a STOP condition

- 2. If a master wants to receive/read data from a slave:

- Master-receiver sends a START condition and addresses the slave-transmitter

- Master-receiver sends the requested register to read to slave-transmitter

- · Master-receiver receives data from the slave-transmitter

- Master-receiver terminates the transfer with a STOP condition

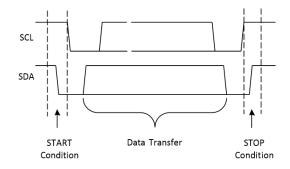

#### **A1.1.1 START and STOP Conditions**

I<sup>2</sup>C communication with this device is initiated by the master sending a START condition and terminated by the master sending a STOP condition. A high-to-low transition on the SDA line while the SCL is high defines a START condition. A low-to-high transition on the SDA line while the SCL is high defines a STOP condition.

Figure A1. Example of START and STOP Condition

#### A1.1.2 Repeated START Condition

A repeated START condition is similar to a START condition and is used in place of a back-to-back STOP then START condition. It looks identical to a START condition, but differs from a START condition because it happens before a STOP condition (when the bus is not idle). This is useful for when the master wishes to start a new communication, but does not wish to let the bus go idle with the STOP condition, which has the

chance of the master losing control of the bus to another master (in multi-master environments).

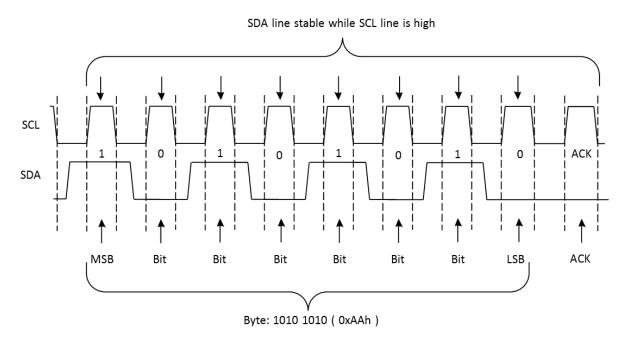

#### A1.2 Data Validity and Byte Format

One data bit is transferred during each clock pulse of the SCL. One byte is comprised of eight bits on the SDA line. A byte may either be a device address, register address, or data written to or read from a slave. Data is transferred Most Significant Bit (MSB) first. Any number of data bytes can be transferred from the master to slave between the START and STOP conditions. Data on the SDA line must remain stable during the high phase of the clock period, as changes in the data line when the SCL is high are interpreted as control commands (START or STOP).

Figure A2. Example of Single Byte Data Transfer

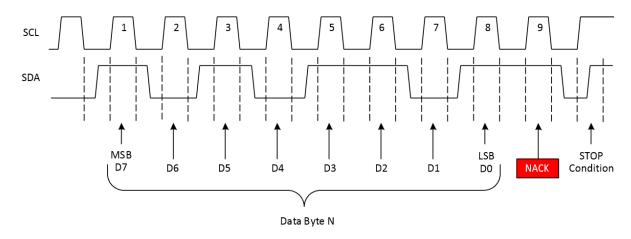

#### A1.3 Acknowledge (ACK) and Not Acknowledge (NACK)

Each byte of data (including the address byte) is followed by one ACK bit from the receiver. The ACK bit allows the receiver to communicate to the transmitter that the byte was successfully received and another byte may be sent.

Before the receiver can send an ACK, the transmitter must release the SDA line. To send an ACK bit, the receiver shall pull down the SDA line during the low phase of the ACK/NACK-related clock period (period 9), so that the SDA line is stable low during the high phase of the ACK/NACK-related clock period. Setup and hold times must be taken into account.

When the SDA line remains high during the ACK/NACK-related clock period, this is interpreted as a NACK. There are several conditions that lead to the generation of a NACK:

- 1. The receiver is unable to receive or transmit because it is performing some real-time function and is not ready to start communication with the master.

- 2. During the transfer, the receiver gets data or commands that it does not understand.

- 3. During the transfer, the receiver cannot receive any more data bytes.

- 4. A master-receiver is done reading data and indicates this to the slave through a NACK.

Figure A3. Example NACK Waveform

#### A2 I<sup>2</sup>C Data

Data must be sent and received to or from the slave devices, but the way that this is accomplished is by reading or writing to or from registers in the slave device.

Registers are locations in the slave's memory which contain information, whether it be the configuration information, or some sampled data to send back to the master. The master must write information into these registers in order to instruct the slave device to perform a task.

While it is common to have registers in I<sup>2</sup>C slaves, please note that not all slave devices will have registers. Some devices are simple and contain only 1 register, which may be written directly to by sending the register data immediately after the slave address, instead of addressing a register. An example of a single-register device would be an 8-bit I<sup>2</sup>C switch, which is controlled via I<sup>2</sup>C commands. Since it has 1 bit to enable or disable a channel, there is only 1 register needed, and the master merely writes the register data after the slave address, skipping the register number.

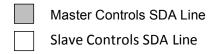

#### A2.1 Writing to a Slave On The I<sup>2</sup>C Bus

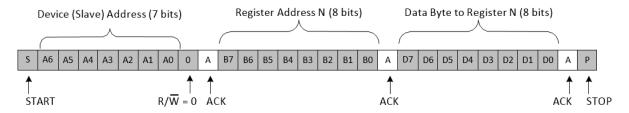

To write on the I<sup>2</sup>C bus, the master will send a start condition on the bus with the slave's address, as well as the last bit (the R/W bit) set to 0, which signifies a write. After the slave sends the acknowledge bit, the master will then send the register address of the register it wishes to write to. The slave will acknowledge again, letting the master know it is ready. After this, the master will start sending the register data to the slave, until the master has sent all the data it needs to (sometimes this is only a single byte), and the master will terminate the transmission with a STOP condition.

Figure A4 shows an example of writing a single byte to a slave register.

#### Write to One Register in a Device

Figure 4. Example I<sup>2</sup>C Write to Slave Device's Register

# A2.2 Reading From a Slave On The I<sup>2</sup>C Bus

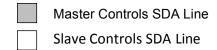

Reading from a slave is very similar to writing, but with some extra steps. In order to read from a slave, the master must first instruct the slave which register it wishes to read from. This is done by the master starting off the transmission in a similar fashion as the write, by sending the address with the R/W bit equal to 0 (signifying a write), followed by the register address it wishes to read from. Once the slave acknowledges this register address, the master will send a START condition again, followed by the slave address with the R/W bit set to 1 (signifying a read). This time, the slave will acknowledge the read request, and the master releases the SDA bus, but will continue supplying the clock to the slave. During this part of the transaction, the master will become the master-receiver, and the slave will become the slave-transmitter.

The master will continue sending out the clock pulses, but will release the SDA line, so that the slave can transmit data. At the end of every byte of data, the master will send an ACK to the slave, letting the slave know that it is ready for more data. Once the master has received the number of bytes it is expecting, it will send a NACK, signaling to the slave to halt communications and release the bus. The master will follow this up with a STOP condition.

Figure A5 shows an example of reading a single byte from a slave register.

#### Read Fro m One Register in a Device

Figure A5. Example I<sup>2</sup>C Read from Slave Device's Register